コンピュータシステム教育用教材の開発・頒布

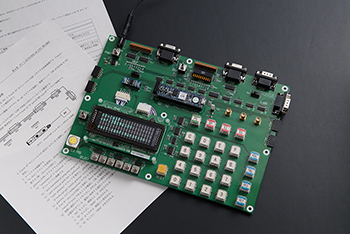

KUE-CHIP2教育システム

KUE-CHIP2教育システムは均整の取れた計算機教育を実現します。

※KUE-CHIP2 は、2025年3月末をもって頒布を完了しました。

概要

計算機入門教育あるいはLSI設計教育を目的とするKUE-CHIP2教育システムを、教育研究機関に頒布しております。

用途

- 計算機入門教育

学生実験などで、マイクロプロセッサの構造と動作の基本原理を体験するのに適しています。プログラミングの例題も豊富にそろっています。 - LSI設計教育

KUE-CHIP2と等価なプロセッサを試作するために必要な設計データが公開されています。また試作したプロセッサの動作テストを行う機能を備えています。

特徴

計算機教育用マイクロプロセッサ:KUE-CHIP2を採用

- 簡素なアーキテクチャと最小限の命令セット

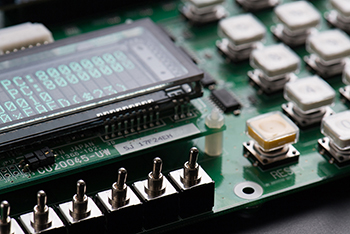

- すべてのレジスタ、カウンタ、フラグの値の表示と書換えが可能

- 1命令、1クロックフェーズ単位でのプログラムの実行/停止を制御

- 幅広いクロック周波数(0.033Hz~1.0MHz)で動作

計算機の構造や動作の基本原理を感じとるのに格好の教材

九州大学 名誉教授 安浦寛人

システムのブラックボックス化が進み、計算機のユーザが計算機の物理的な構造に直接触れる機会が少なくなっています。計算機教育においても、ハードウェアに関する知識は、論理回路、計算機構成論などの講義による知識を、簡単な論理回路による実験と市販の1チップCPUを用いた実験で確認する形で行われることが一般的かと思われます。このため学生は、計算機アーキテクチャと論理回路や電子回路との関連が理解できなかったり、プログラムを書く立場から自分なりに理解している計算機アーキテクチャにどことなく不安を感じることが少なくないようです。

KUE-CHIP2教育システムは、計算機の内部構造を見て触れることが出来るように設計されており、計算機の構造や動作の基本原理を学生が肌で感じとるのに格好の教材です。計算機工学の均整の取れた教育のためには、さらには、集積回路設計の教材として、KUE-CHIP2教育システムをお薦めします。

計算機入門教育カリキュラムの例

学校/九州大学工学部電気系学科

- 期間/通年

- 対象/学部3回生

- 目的/KUE-CHIP2のアーキテクチャを理解した上で、KUE-CHIP2と同じ仕様のマイクロプロセッサの設計、試作を行なう

KUE-CHIP2教育用ボードを使った実験

- 内容/KUE-CHIP2マイクロプロセッサのレジスタ、フラグ、バス、制御線の予測および観測

- 時期/前期

- 回数/学生実験5回(1回2時間20分)

KUE-CHIP2と同じ仕様のマイクロプロセッサの設計

- 内容/「KUE-CHIP2設計ドキュメント」の論理式を除いた仕様を与え、その論理式を導くと共に、ICを用いて回路を設計、論理回路用CADを用いてシミュレーションを行なう

- 時期/前期

- 回数/学生実験4回(1回2時間20分)+夏休みの宿題

KUE-CHIP2と同じ仕様のマイクロプロセッサの制作

- 内容/74シリーズのTTL ICをラッピングで配線する

- 時期/後期

- 回数/学生実験14回(1回2時間20分)

お知らせ

KUE-CHIP2 は、2025年3月末をもって頒布を完了しました。

KR-CHIP 教育システム

大学等の教育機関または企業の新人教育の教材として KR-CHIP 教育システムを開発しました。

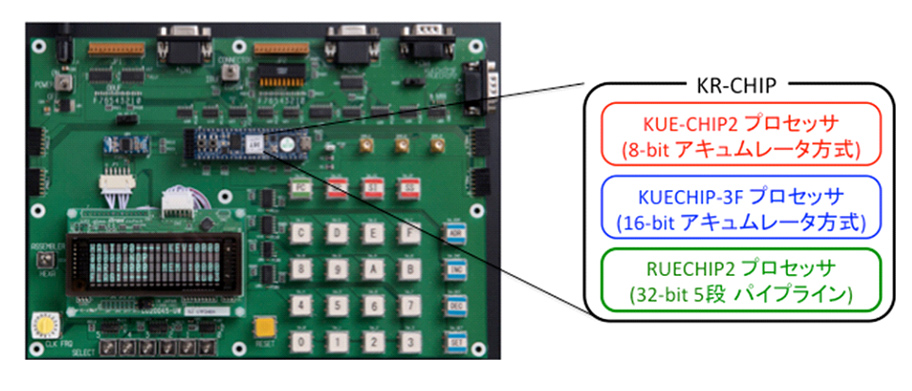

KR-CHIP 教育用ボードと KR-CHIP

概要

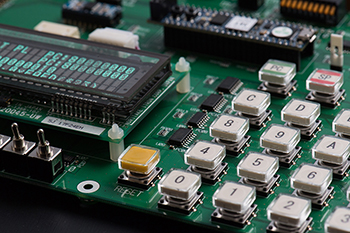

KR-CHIP 教育用ボードは、8bit, 16bit, 32bit の3種類のマイクロプロセッサを搭載した、学生実習や新人研修向けのワンボード・コンピュータです。

アセンブリ言語を用いてベアメタル・プログラミングを行い、プロセッサ内部での命令の解釈/実行を観測することで、計算機の動作原理を理解することを目的としています。

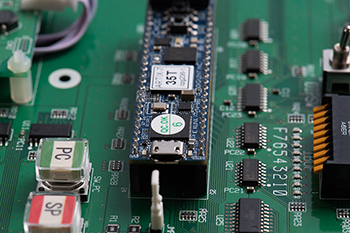

KR-CHIP は、これまで数十大学で使用されてきた KUE-CHIP2 教育システム への教育現場からの要望を反映することを目的に、Xilinx FPGA で新たに実現した計算機教育専用のプロセッサです。

用途

計算機入門教育

学生実験などで、マイクロプロセッサの構造と動作の基本原理を体験するのに適しています。プログラミングの例題も豊富にそろっています。

LSI設計/FPGA設計教育

KR-CHIP に搭載されている3種類のマイクロプロセッサをFPGAで試作し、その動作を確認するために必要な設計データを公開しています。

搭載する3種類のプロセッサについて

1. KUE-CHIP2

- 8bit アキュムレータ方式の簡素なアーキテクチャと最小限の命令セットを備えたプロセッサ。

- KUE-CHIP2 教育システム を用いた学生実習等の教育カリキュラムを継続するのに適しています。

- 「遠隔講義/自宅学習」用に、Webブラウザ上で動作する「命令シミュレータ/アセンブラ」が公開されています。

2. KUECHIP-3F

- KUE-CHIP2 を16bit 化し、SP (Stuck Pointer) レジスタを追加したプロセッサ。

- サブルーチンコールを用いて、16bit メモリ空間のアセンブラ・プログラミングを学習するのに適しています。

- 「遠隔講義/自宅学習」用に、Webブラウザ上で動作する「命令シミュレータ」が公開されています。

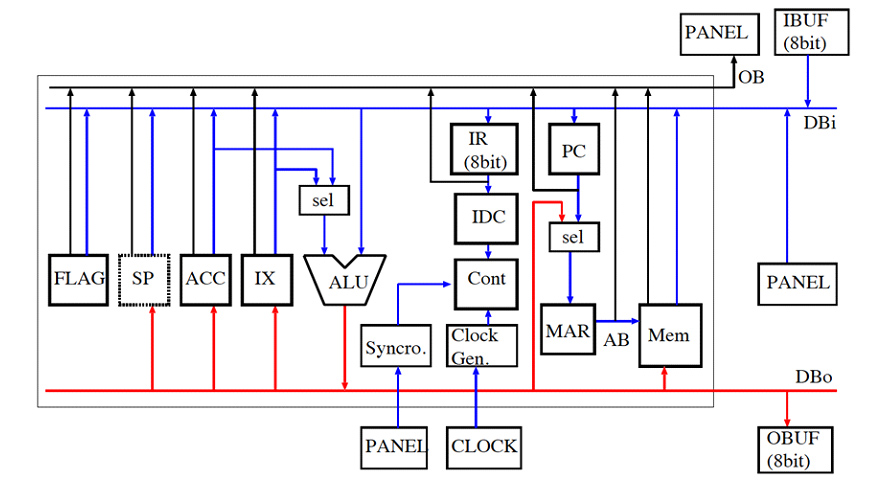

KUE-CHIP2とKUECHIP-3F のブロック図 (SP レジスタは KUECHIP-3F のみ搭載)

3. RUECHIP2

- パターソン/ヘネシーの教科書「コンピュータの構成と設計」の 32bit 5段パイプライン・プロセッサ。

- MIPS命令のパイプライン処理/データのフォワーディングを観測し、その動作原理を理解することに適しています。

- GCC (Gnu C Compiler) ベースのクロスコンパイラを用いた組込みプログラミングを体験できます。

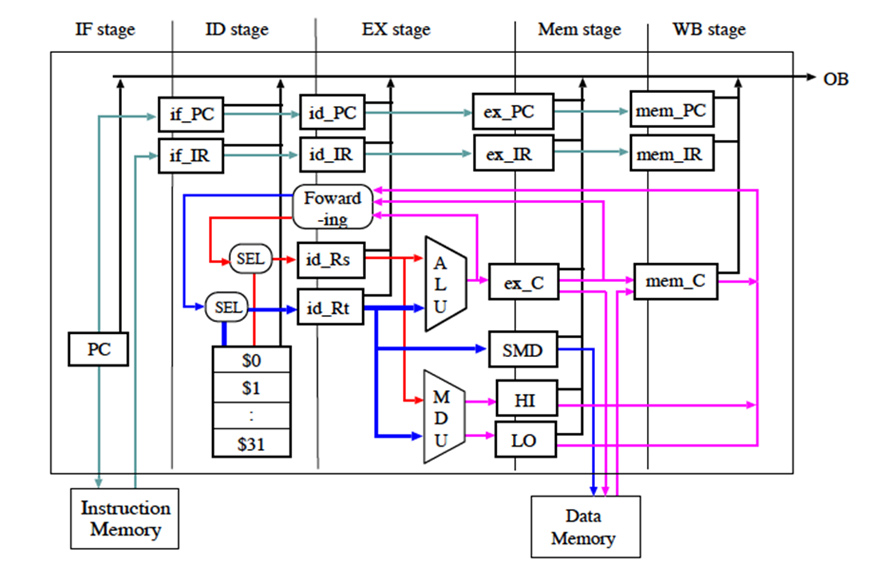

RUECHIP2 のブロック図

特徴

- 内部のすべてのレジスタ、カウンタ、フラグの値を外部から観測可能

- 1クロックフェーズ単位でのプログラムの実行/停止を制御

- 幅広いクロック周波数(0.1Hz〜10MHz)で動作

KR-CHIP 教育システムは、ライセンシング先であるカグデン合同会社にて頒布しています。

お問い合わせ先

カグデン合同会社

![]()